Advanced Physical Design Training is a 4.5-month program for working professionals to master the full Physical Design flow (Netlist to GDSII) at the 14nm node. It includes hands-on training with Synopsys and Cadence tools, 24×7 tool access, and 100% placement support.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

Advanced Physical Design Training Overview

Course Overview

Advanced Physical Design Training – Summary

Duration: 5 months advanced program

Tools: Synopsys Custom Compiler and Cadance Virtuoso (DC, ICC II, StarRC, PT, ICV)

Placement Support: Institute provides placement support till candidate gets a JOB

Training Highlights:

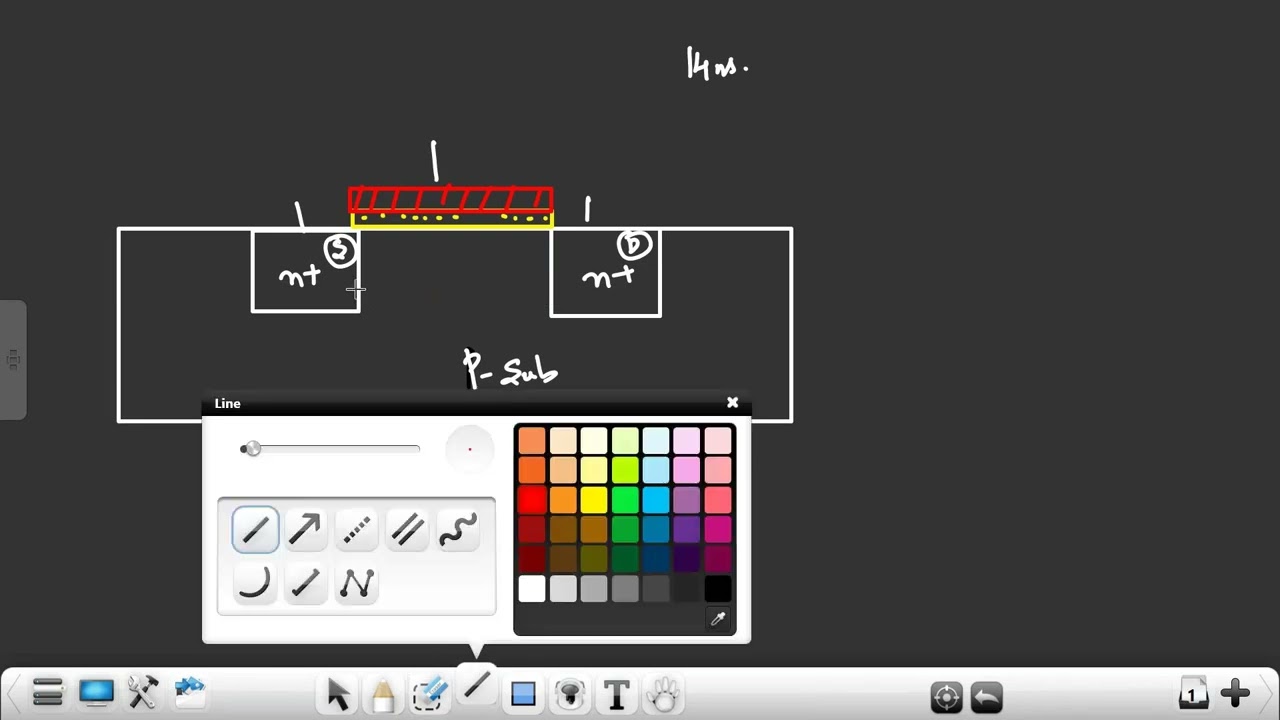

Advanced Physical Design flow from Netlist to GDSII at 14nm

Designed specifically for working professionals

Assumes prior knowledge of CMOS, Digital Design, and Fabrication

Hands-on training using industry-preferred Synopsys Custom Compiler and Cadance Virtuoso tools

Focus on critical industry issues and practical debugging methods

Technical Coverage:

Complete Physical Design Flow: Synthesis to GDSII

IR Drop Analysis and Power Integrity Techniques

Physical Verification using ICV

Timing Analysis using PrimeTime

Place & Route using ICC II and extraction using StarRC

Hands-on Training:

Multiple real-time projects using Synopsys Custom Compiler and Cadance Virtuoso Tools

Debug and optimization of real-world PD issues

Industry scenarios for floorplanning, placement, CTS, routing, and closure

Training Delivery:

Focused theory with in-depth lab sessions

Training delivered by experienced industry professionals

Program Highlights:

Designed to upskill professionals for 14nm and below process nodes

Emphasis on practical issues, power integrity, and closure techniques

Real-time debug-oriented training with job-ready assignments

Institute Info:

Offered by VLSIGuru, established in 2012

Trained over 10,000+ students

Affordable in-class training in Bangalore

Online training available for students outside Bangalore

Detailed overview:

Advanced Physical Design Training is a 5 months course meant for working professionals to gain in-depth knowledge of all aspects of Physical design flow from Netlist to GDSII including all the aspects of Physical design flow at 14nm. Course assumes that student is familiar with fundamental concepts of Physical design like CMOS, Digital design and fabrication. Course involves multiple hands on projects using Synopsys Custom Compiler and Cadance Virtuoso tools(DC, ICC II, Star RC, PT, ICV). Synopsys Custom Compiler and Cadance Virtuoso flow is among widely used PnR flow in industry.

Physical Design training emphasizes on issues faced in industry level projects and how to resolve those issues. Training also focus on other aspects of VLSI back end flow including Synthesis, IR drop analysis and Physical verification. Training will provide participants with expertise on entire back end flow, making sure that candidate fits in to various job requirements.

SYNOPSYS,CADENCE {synopsys ICC II, RedHawk, Primetime, StarRC, Design Compiler, ICV}

Key Features

Who All Can Attend This Advanced Physical Design Training?

This training is ideal for VLSI professionals and graduates aiming to specialize in back-end design at advanced technology nodes. It’s best suited for those involved in layout, timing, and physical implementation of SoCs.Pre-requisites To Take Advanced Physical Design Training

- Good understanding VLSI Technology basics(CMOS, FinFET, etc)

- Digital design concepts

High Demand for Advanced Physical Design Training

Know about the Growing VLSI industry

Physical Design Engineers are critical for RTL to GDSII implementation. Engineers skilled in floorplanning, placement, clock tree synthesis (CTS), routing, and signoff analysis at advanced nodes (14nm, 7nm) see faster career growth. Familiarity with tools like ICC2, Innovus, and PrimeTime boosts salary potential.

₹7 LPA

₹12 LPA

₹16 LPA

₹20 LPA

₹28 LPA

Mode of Training

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

- Learn in real-time with instructor-led sessions

- Flexible access from anywhere

- Recorded sessions available for revision

- Training on industry-standard tools

- Get certification after completion

- Self-paced learning as per your flexibility

- Industry-aligned learning modules

- Certification after course completion

- Access to structured video lessons and materials

- Track your progress step by step

- Access to learning materials for more than 1.5 years

This Advanced Physical Design Training is crucial for working professionals aiming to master the complexities of modern VLSI implementation down to 14nm. It offers hands-on experience with industry-standard Synopsys tools and focuses on solving real-world challenges in the physical design flow from netlist to GDSII. The comprehensive curriculum ensures expertise across the entire back-end process, enhancing career prospects in the dynamic VLSI industry.

Career Path

Learning Path

At VLSIGuru, we believe that education should lead to meaningful employment. Our training programs are designed not just to impart technical excellence, but also to bridge the gap between academic learning and industry demands. With a strong network of hiring partners and a proven track record, we ensure that our students are career-ready.

Placement Highlights

- Industry-aligned curriculum

- Hands-on projects and case studies

- Communication skills

- Resume building and interview preparation

- Technical and HR mock sessions

- Aptitude and domain-specific test series

- Regular drives and exclusive hiring events with partner companies

- Resume building and interview preparation

At VLSIGURU, we provide industry-focused VLSI training and guidance that helps students and professionals build strong technical skills and succeed in their careers. Our programs are designed to be practical, flexible, and aligned with current industry requirements.

Student Reviews

Frequently Asked Questions

- Course presentations for all topics

- Session notes

- Lab documents with detailed steps

- User guides

- Yes, Course fee also includes support for doubt clarification sessions even after course completion

- You have option to mail you queries

- Option to meet in person to clarify doubts

- Most of the time, the reasoning for any institute to charge a higher fee(excess of 1 lakh) is too high. It is not true.

- VLSIGuru believes in creating an educational model that is affordable and sustainable in the long run. We have been running successfully since we started training in 2012 with 3500+ students trained so far. We take pride in the fact that it is VLSIGuru which makes other institutes also offer courses in the 30K to 50K range, otherwise it used to be much higher.

- Institute owns the office facility, hence we avoid rental expenses. Keeping it aside, we also find it difficult to comprehend why the course fee should be in excess of 1 Lakh.

- Good understanding VLSI Technology basics(CMOS, FinFET, etc)

- Digital design concepts

Each session of course is recorded, missed session videos will be shared

- Yes, You will have option to view the recorded videos of course for the sessions missed

- You will have option to repeat the course any time in next 1 year

You'll gain deep expertise in advanced physical design flow (Netlist to GDSII at 14nm), timing constraints, power planning, placement, routing, STA, and physical verification – crucial for modern VLSI.

The course offers extensive hands-on experience with industry-standard Synopsys tools (DC, ICC II, StarRC, PT, ICV), making you proficient with the leading technology in the field.

Expect significant practical learning through multiple real-time projects and labs using the Synopsys implementation flow, directly addressing real-world PD challenges.

You'll learn the entire flow comprehensively, from initial netlist to final GDSII, including floorplanning, placement, routing, clock tree synthesis, and verification.

While RTL design focuses on the functional description, this course delves into the physical realization of the design on silicon, a specialized and critical downstream process.

Physical design is the crucial stage that transforms a circuit design into a manufacturable chip layout, directly impacting performance, power, and cost – making it a vital specialization.

You'll master advanced physical design implementation, timing closure, power integrity, congestion management, and physical verification – essential for successful VLSI careers.

Beyond skills, we provide placement support until you secure a job, leveraging your enhanced expertise in high-demand areas like 14nm physical design.

This training opens doors to roles like Physical Design Engineer, Layout Engineer (Advanced), and Physical Verification Engineer, with strong career growth potential in the booming VLSI sector.

This intensive 4-month advanced program is structured to efficiently impart comprehensive knowledge without excessively disrupting your professional commitments.

Yes, the training strongly emphasizes resolving issues encountered in real industry projects, equipping you with practical debugging and optimization methodologies.

Effective floorplanning is fundamental for optimizing chip area, wirelength, and performance, and this course provides in-depth knowledge of its advanced techniques.

We understand the needs of working professionals and strive to offer flexible learning options, including potential online access and recorded sessions for missed content.

This course assumes and builds upon basic concepts, diving into advanced techniques and industry best practices relevant to complex, cutting-edge designs.

© 2025 - VLSI Guru. All rights reserved

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.